CIESコンソーシアム

国家プロジェクトJSPS研究拠点形成事業

半導体集積デバイス向け二次元電子・スピン材料研究拠点

コーディネーター

遠藤 哲郎

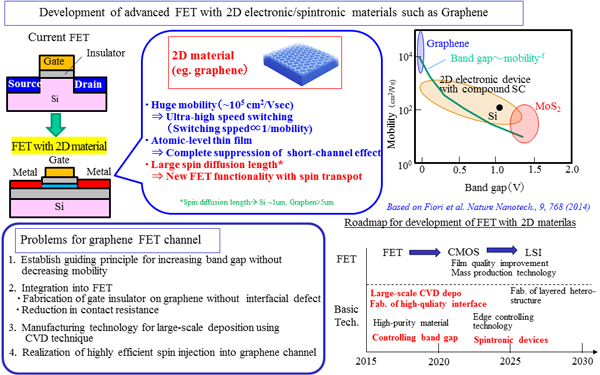

電子を情報単体とする情報処理デバイスのスケーリングは限界に近づいており、次世代の半導体開発のブレークスルーとなる新材料と、その製造技術へのインテグレーション技術の開発が、強く求められています。グラフェンに代表される2次元材料は、高い電子移動度を有するにのみならず、室温で非常に長いスピン拡散長を有し、現在のMOSチャネルにかわる新規電子伝導チャネルとして、さらに近年電子にかわる超低消費電力の新しい情報担体として注目されているスピンの伝導チャネルとして、大きな注目を集めています。しかしながら、グラフェン等の2次元材料を集積回路へ導入する製造技術はいまだ確立していないため、現状ではその応用範囲はニッチな産業領域に限られています。本課題の日本における代表拠点研究機関である東北大学国際集積エレクトロニクス研究開発センターは、平成24年に設立されて以来、縦型半導体からスピン応用ロジック・メモリまで、最先端の半導体デバイスの開発を先導してまいりました。

本課題では、英国の拠点研究機関であるケンブリッジ大学、ならびにフランスの代表拠点研究機関であるパリ南大学、日本の協力機関である東北大学工学研究科、東京大学、および筑波大学、ならびに英国の協力機関である日立ケンブリッジ研究所などの世界トップレベルの研究機関間の緊密な連携により、CVD技術を駆使した再現性の高い2次元電子材料の製造技術、および高品質な電極物質や絶縁体との界面を創製技術を開発することで、高品質の2次元電子、スピンチャネルを実現し、前記チャネルを伝導する電子・スピンの挙動を理論的、実験的に解明することを目指します。さらに、本課題の共同研究によって次世代半導体のブレークスルー技術を創製するとともに、研究拠点交流を通じて革新的技術創出に資する国際的なセンス豊かな若手研究者を育成することも目標とします。